# **Detector Support Group**

We choose to do these things "not because they are easy, but because they are hard". Weekly Report, 2021-12-01

## **Summary**

### <u>Hall A – SoLID</u>

Mary Ann Antonioli, Pablo Campero, Brian Eng, Mindy Leffel, and Marc McMullen

- Completed drawing A00000-16-03-0000, an index of drawings

- Converting EPICS CSS-BOY screens to CSS Phoebus screens

- Fabricated 19 cables: 16 ferrule-to-ferrule and three ferrule-to-DB9 connector

#### <u>Hall B – RICH-II</u>

Mary Ann Antonioli, Peter Bonneau, Pablo Campero, Brian Eng, George Jacobs, Tyler Lemon, and Marc McMullen

- Testing hardware interlock system RMC

- \* Created prototype adapter to connect 37-pin IDC header to breadboard

- \* Verifying voltages and signal routing through RMC to sensor PCB are correct

- Contacted hardware interlock chassis fabricator, Par-metal, to procure two chassis

- Fabricated four Molex cables; 17 of 24 complete

- Populating one of two backplane PCBs (~25% complete)

Backplane PCB top and bottom layers

#### <u>Hall C – NPS</u>

Mary Ann Antonioli, Peter Bonneau, Aaron Brown, Pablo Campero, Brian Eng, George Jacobs, Mindy Leffel, Tyler Lemon, and Marc McMullen

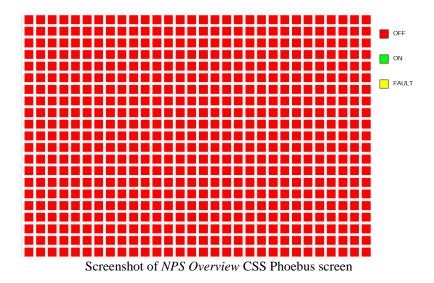

• Developed Python script to generate NPS Overview Phoebus screen

#### Detector Support Group We choose to do these things "not because they are easy, but because they are hard". Weekly Report, 2021-12-01

- Screen features an embedded display for each PMT channel that changes color to indicate if channel is on, off, or in a fault state

- ★ Each embedded display, when clicked, opens a pop-up window (*PMT Status*) that details the nature of the fault and displays readback voltage and current

- Developed IronPython script, in Ansys, to export temperature probe values to a text file

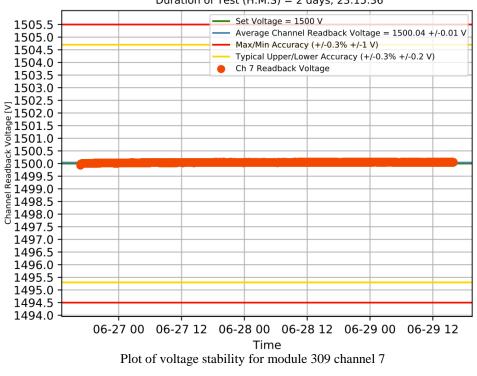

- Developed Python script to generate voltage stability plots for all channels of a module to be included in the DSG testing & analysis MariaDB database

Stability Test 1500 V [With Load]: Trial #1, Crate #2, Slot #9, Board #309 Duration of Test (H:M:S) = 2 days, 23:15:36

> 2 DSG Weekly Report, 2021-12-01

- Developed list of LabVIEW programs needed for the hardware interlock system

- Worked on ESR film pre-shaping 320 of 600 completed (~55%)

#### **EIC**

Pablo Campero, Brian Eng

- Generated, using NX12, new simplified model of Be beam pipe and Si sensor L1 and imported to Ansys

- ★ Shortened the length of the Be pipe from 1470 mm to 320.5 mm; the same length as the Si sensor L1

- \* Performing calculations and evaluating/verifying results